hipSYCL Sees Work-In-Progress Support For Intel oneAPI Level Zero Backend

The open-source hipSYCL project already supports SYCL CPU-based execution via OpenMP, targeting NVIDIA GPUs using CUDA, and targeting AMD Radeon graphics using HIP/ROCm. Now with a new work-in-progress back-end is support for Intel graphics using Level Zero. The hipSYCL project is one of several SYCL implementations aiming to support various CPUs and GPUs/accelerators while so far it's been one of the most diverse. The hipSYCL project supports most of SYCL 2020 at present.

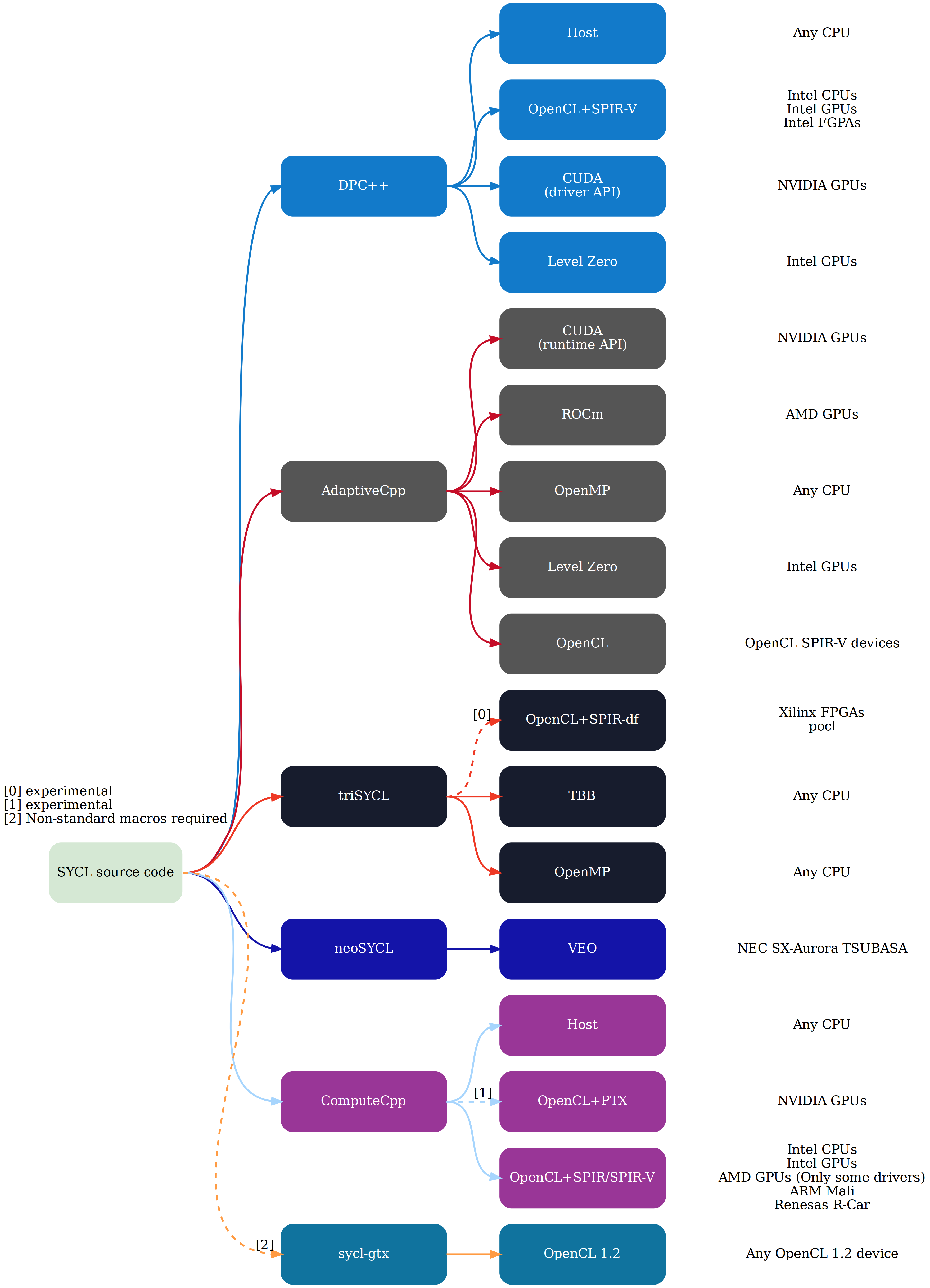

hipSYCL in its current position prior to merging Intel L0 support.

The current Intel Level Zero back-end for hipSYCL was devised by Aksel Alpay of Heidelberg University. It is currently "highly experimental" but the basics should be working while still to be handled is local memory, group algorithms, reductions, and other features. The SPIR-V compilation for this back-end is handled using the Clang SYCL front-end.

More details on this notable hipSYCL work can be found via this pull request. While still experimental, the hope is to begin merging the code sooner rather than later.

12 Comments