Phoronix: Ampere Altra Max Continues To Deliver Competitive Power Efficiency To AMD EPYC & Intel Xeon

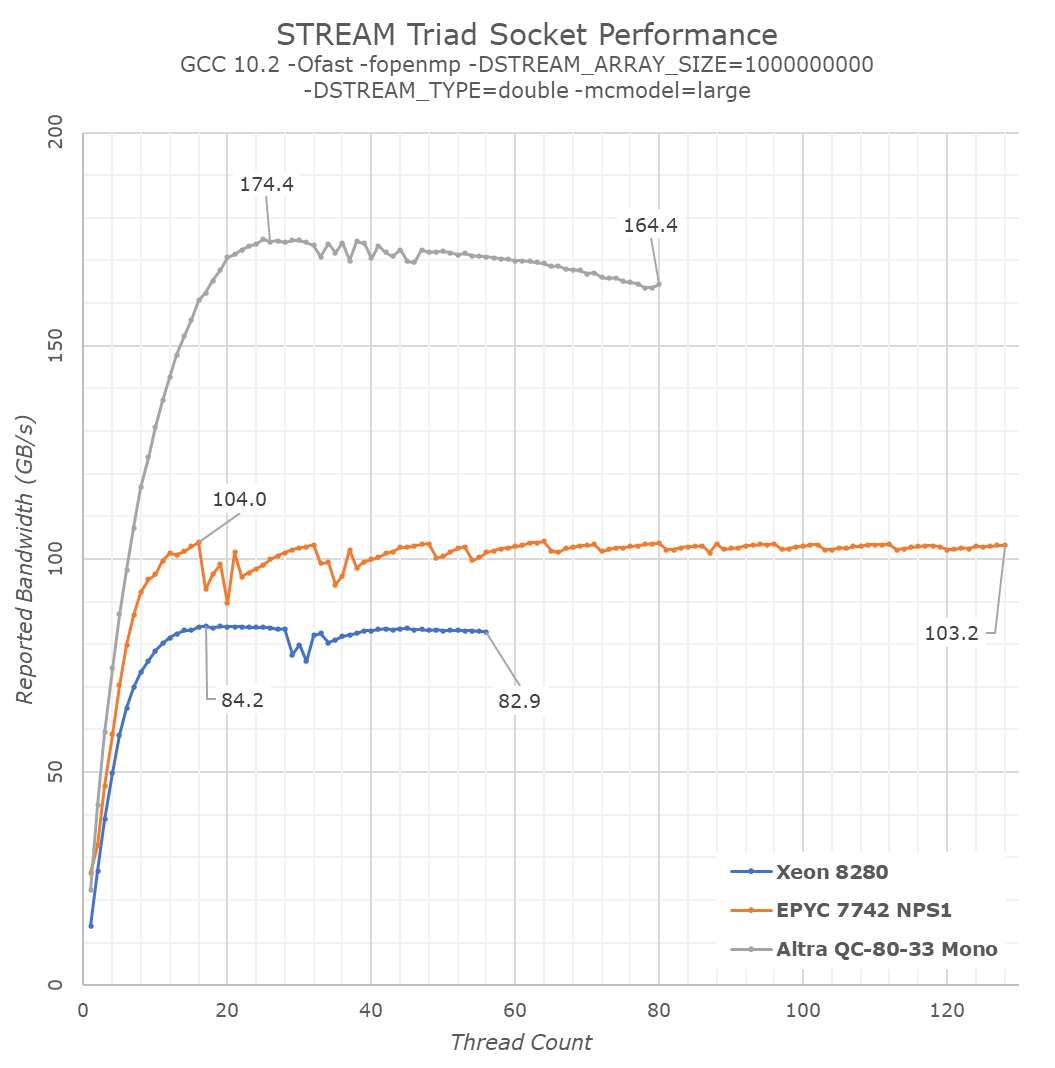

While it's been three years now since Ampere Altra Q80 was first introduced and two years since first testing the 128-core Ampere Altra Max, this ARM server platform has aged rather well with more robust hardware platforms coming to market with better firmware, the AArch64 Linux/open-source software ecosystem as a whole improving a lot during this time and more open-source projects receiving ARM optimizations, and other improvements made. While we're eagerly awaiting to see AmpereOne hardware, here is a look at how Ampere Altra Max M128-30 is standing up against current AMD EPYC Genoa(X) and Bergamo server CPUs along with Intel Xeon Scalable Sapphire Rapids processors in raw performance and power efficiency.

While it's been three years now since Ampere Altra Q80 was first introduced and two years since first testing the 128-core Ampere Altra Max, this ARM server platform has aged rather well with more robust hardware platforms coming to market with better firmware, the AArch64 Linux/open-source software ecosystem as a whole improving a lot during this time and more open-source projects receiving ARM optimizations, and other improvements made. While we're eagerly awaiting to see AmpereOne hardware, here is a look at how Ampere Altra Max M128-30 is standing up against current AMD EPYC Genoa(X) and Bergamo server CPUs along with Intel Xeon Scalable Sapphire Rapids processors in raw performance and power efficiency.

Comment