Originally posted by duby229

View Post

Announcement

Collapse

No announcement yet.

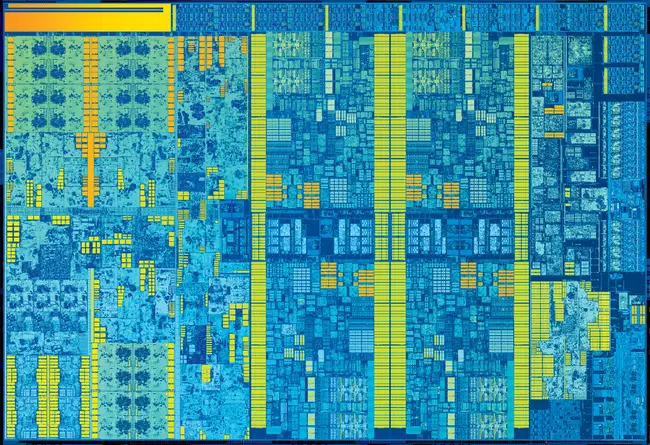

Cleaning Up A Mess: Linux 6.9 Likely To Land Rework Of x86 CPU Topology Code

Collapse

X

-

This is Intel's new strategy. Remember Itanium? Shift the burden to the compiler, who cares if said compiler is essentially impossible to write. Call the whole thing brilliant, and then blame the software when it doesn't work in the real world.Originally posted by ddriver View PostThank intel and its fake marketing cores. But I'd say 2 types of fake cores is simply not enough. It has to be a real maze, a paradoxical issue for the OS to schedule work properly.

Comment

-

No, VISC and Softcore IP never made it into the intel core architecture.Originally posted by sophisticles View Postdrakonas777 and WorBlux

i take it you don't realize that what I suggested was an extension of what Skylake was already doing:

Intel's new Skylake processors have a major update when it comes to single threaded performance, dubbed 'inverse hyper threading'.

Intel's new Skylake processors have a major update when it comes to single threaded performance, dubbed 'inverse hyper threading'.

As I said, cores are an artificial construct, what is the difference between a single core CPU that has 2 ALUs and 2 FPUs and a dual core CPU that has 1 ALU and 1 FPU per core?

The correct answer is none.

In both cases the chip can handle 2 integer based threads and 2 floating point based threads.

If anything the single core chip will be faster because of the unified cache.

Understand?

Also VISC was premised on the idea of the compiler finding and issuing explicit micro-threads based on data flow analysis, and being able to run some of them speculatively.

Skylake was mostly just an iteration on Haswell, with bigger everything, and was about the point when there was enough decodes and u-Op dispatch to make hyper-threading mostly unoticable on control/branch/logic heavy code.

As to a big hyperthread vs a smaller single threaded core... which is faster really depends on the workload. Unified cache could be great, or it could mean data is evicted to the L2 or L3 at the worst possible time, and smaller caches are faster. Also scaling isn't linear... a lot of stuff is on order n*log(n), or

n^2 complexity. ... hence the need for a 3-d architecture to even attempt a 40-60 issue superscaler design.

- Likes 1

Comment

Comment