Originally posted by bridgman

View Post

Whoah...I just now caught that !! Really ??

Ok....so. A: When do you anticipate that AMD dGPUs will ACTUALLY catch up to your APU's of 2014 and in what way?

And.........B: What does this entail for AMD's APU's going forward particularly the upcoming Zen3 / RDNA 2 based "Cezanne" APU's ?

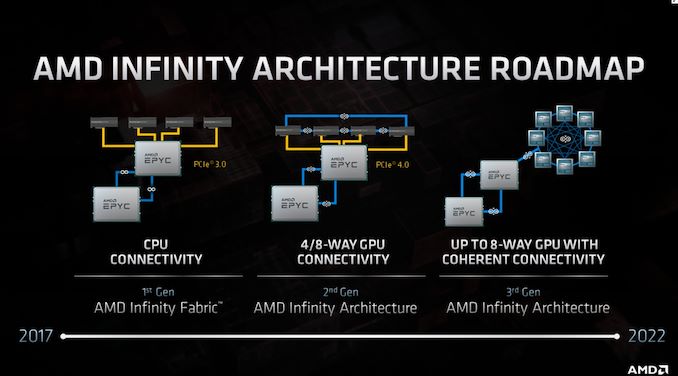

Oh...let me add C: Does Zen 4 / Genoa / 3rd Gen Infinity Architecture herald this "catching up with the APU capabilities we had in 2014" ?

Comment