Originally posted by pkese

View Post

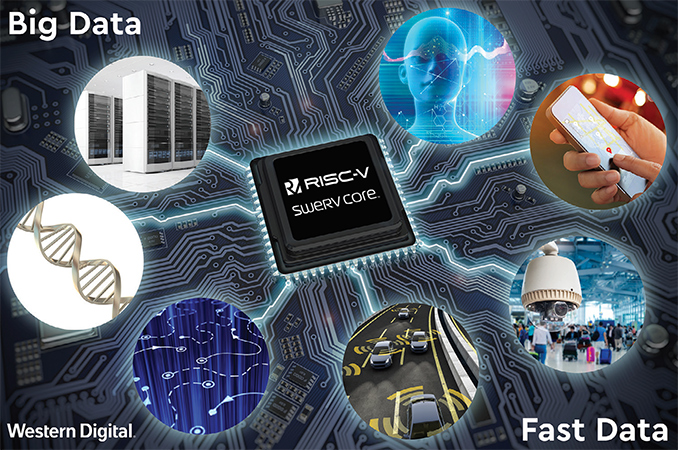

Though that very likely will change in the near future (due to RISC-V mainly).

Can any company besides Intel and AMD even make X86 CPUs?

There's 2 other X86 CPU companies right now: Zhaoxin, which uses the old VIA x86 license, and THATIC, which is joint-venture between AMD and a consortium of Chinese companies under the direction of the Communist Party.

This is highly interesting:

how is RISC-V architecture flawed compared to others when all that RISC-V is is an instruction set?

how is RISC-V architecture flawed compared to others when all that RISC-V is is an instruction set?

Comment