Originally posted by coder

View Post

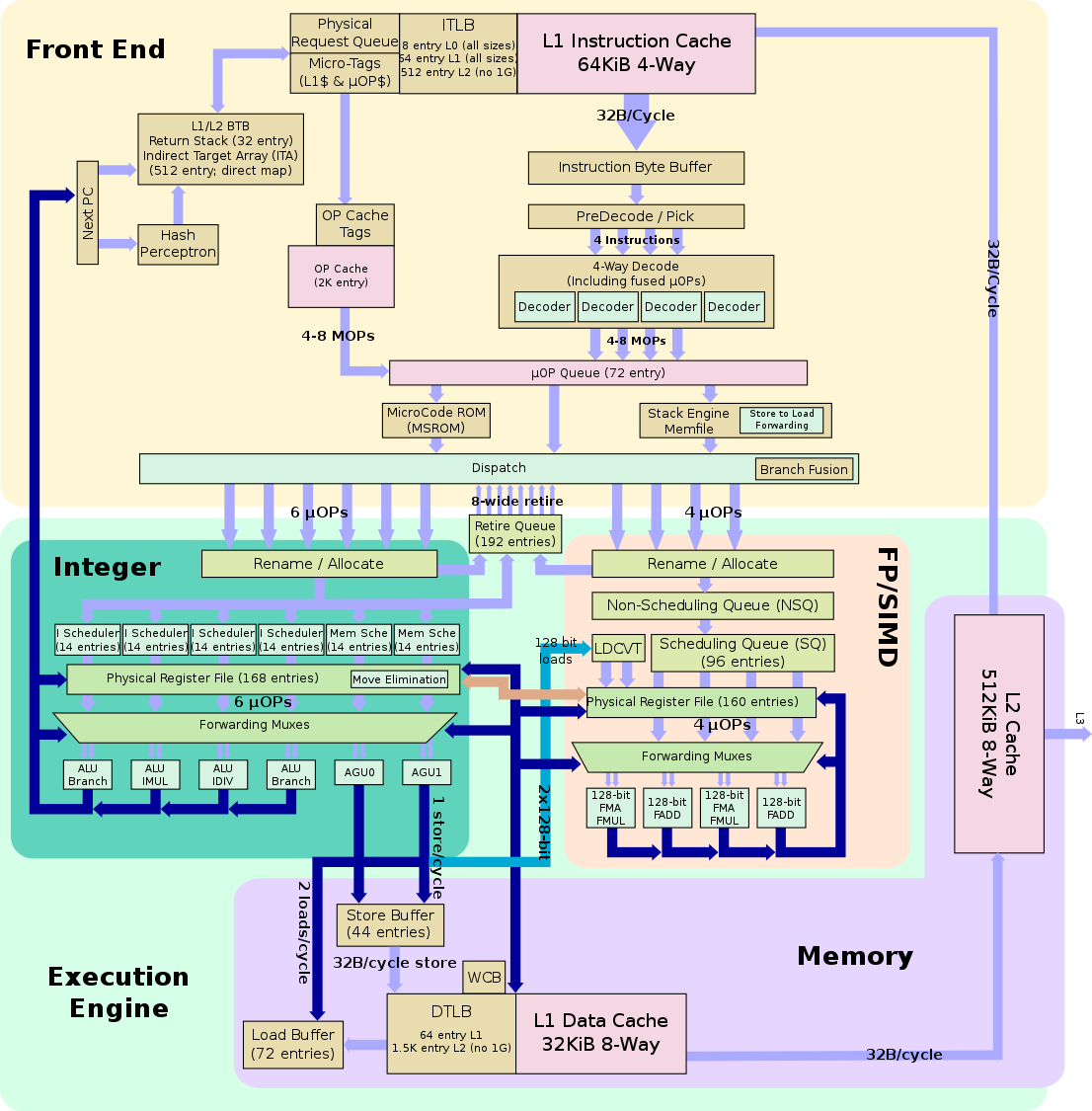

As for the communication of this as a strategic defense against sidechannel attacks; those sorta date back to the confusion around when Spectre was first being widely publicized. There were a bunch of people who asked vendors of in-order RISC-V cores if their cores were vulnerable to certain such attacks, and their answer was no; the press then took that to the public. Then, not long after that, a number of RISC-V vendors rather publicly started collaborating on mitigating these attacks. The combination of the two has created a meme that vulnerable RISC-V cores should not be deployed, and indeed they have not; and it is unlikely, if there are viable mitigations which apply to OoO cores, that those mitigations will not be included with commercially available RISC-V OoO cores as they come out.

So yes, it's probably an exaggeration, but it isn't untrue, nor is it misleading. And FWIW, these cores are on the upper end of in-order performance, especially at the sorts of frequencies they manage to run at. If you are embedding a core and need this sort of performance profile, and want SMP, and want Linux/FreeBSD/FreeRTOS, and also want not to be susceptible to the majority of these recently-popular sidechannel attacks, then these cores could be a very enticing option for you on the merits.

Comment